Apple veut prendre « King Fried Chips » pour visiter Jurassic Park Philosophie dure

Il existe encore de nombreuses énigmes concernant la série de puces M1 développées par Apple.

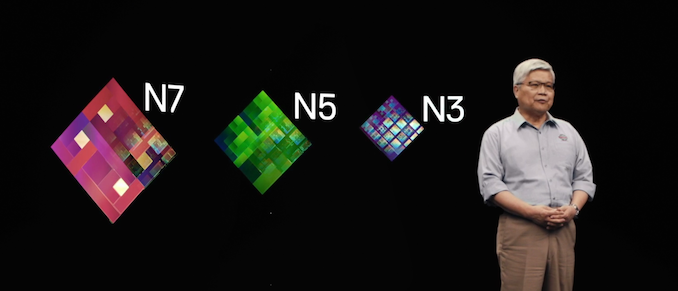

Tout récemment, de nombreuses rumeurs ont circulé sur le suivi des puces M1, M2 et M3, mais la plupart d'entre elles sont des informations qui attirent le regard. Il n'y a pas d'informations claires sur l'architecture, les performances et le cœur, mais plus sur TSMC Mise à niveau des nœuds de processus.

▲ M1 n'est pas encore terminé, M2 et M3 pourraient arriver bientôt. Photo de: progamer

Les technologies de traitement 4 nm, 3 nm et autres nouvelles technologies de TSMC peuvent être des points de mise à niveau plus importants. De cette façon, dans la série M1 qui a déjà un rapport de consommation d'énergie étonnant, M2 et M3 ne font qu'augmenter.

Mais, après deux ans, quand le processus de nœud est-il mis à niveau à 3 nm ?

Il y en a environ deux, l'un consiste à sécher le processus de nœud à 1 nm, en s'approchant sans fil de la limite physique, mais c'est plus difficile. L'autre consiste à contourner les avantages des mises à niveau des processus de nœud et à emprunter le chemin des "petites puces" de Chiplet.

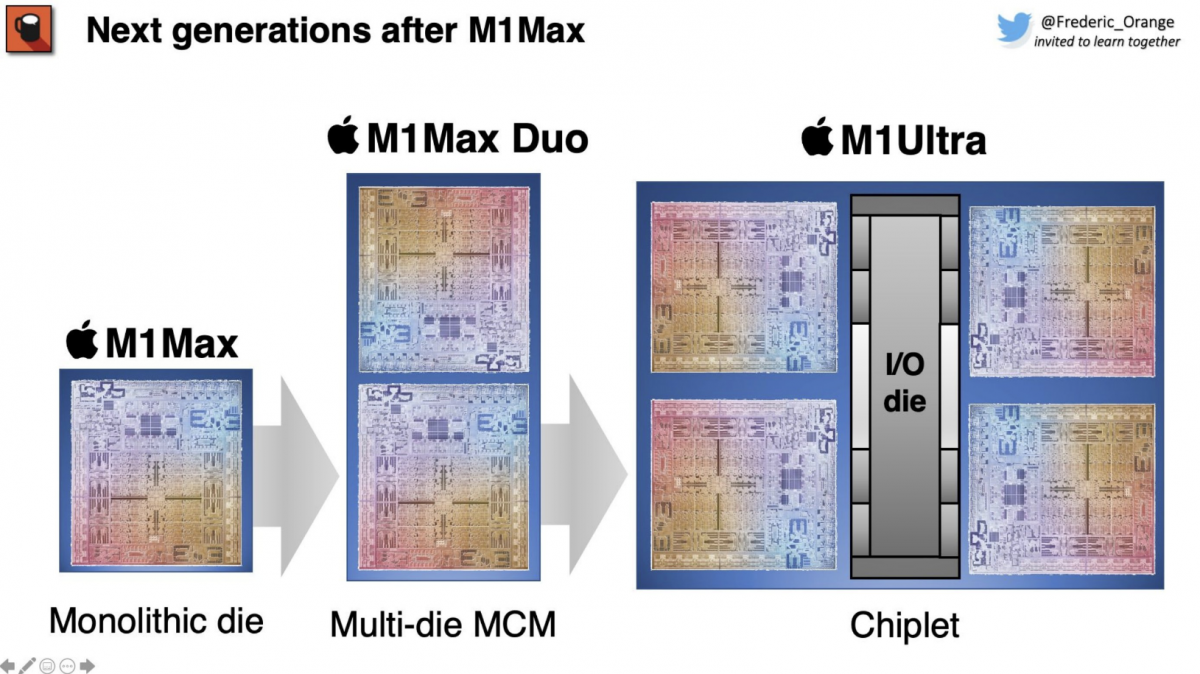

Un M1 Max ne suffit-il pas ? Installez ensuite deux Mac Pro

Cependant, Apple, qui a toujours détesté être à la merci de la chaîne d'approvisionnement, cherche peut-être un moyen réalisable tout en profitant du ratio d'efficacité énergétique élevé des nœuds et des puces ARM.

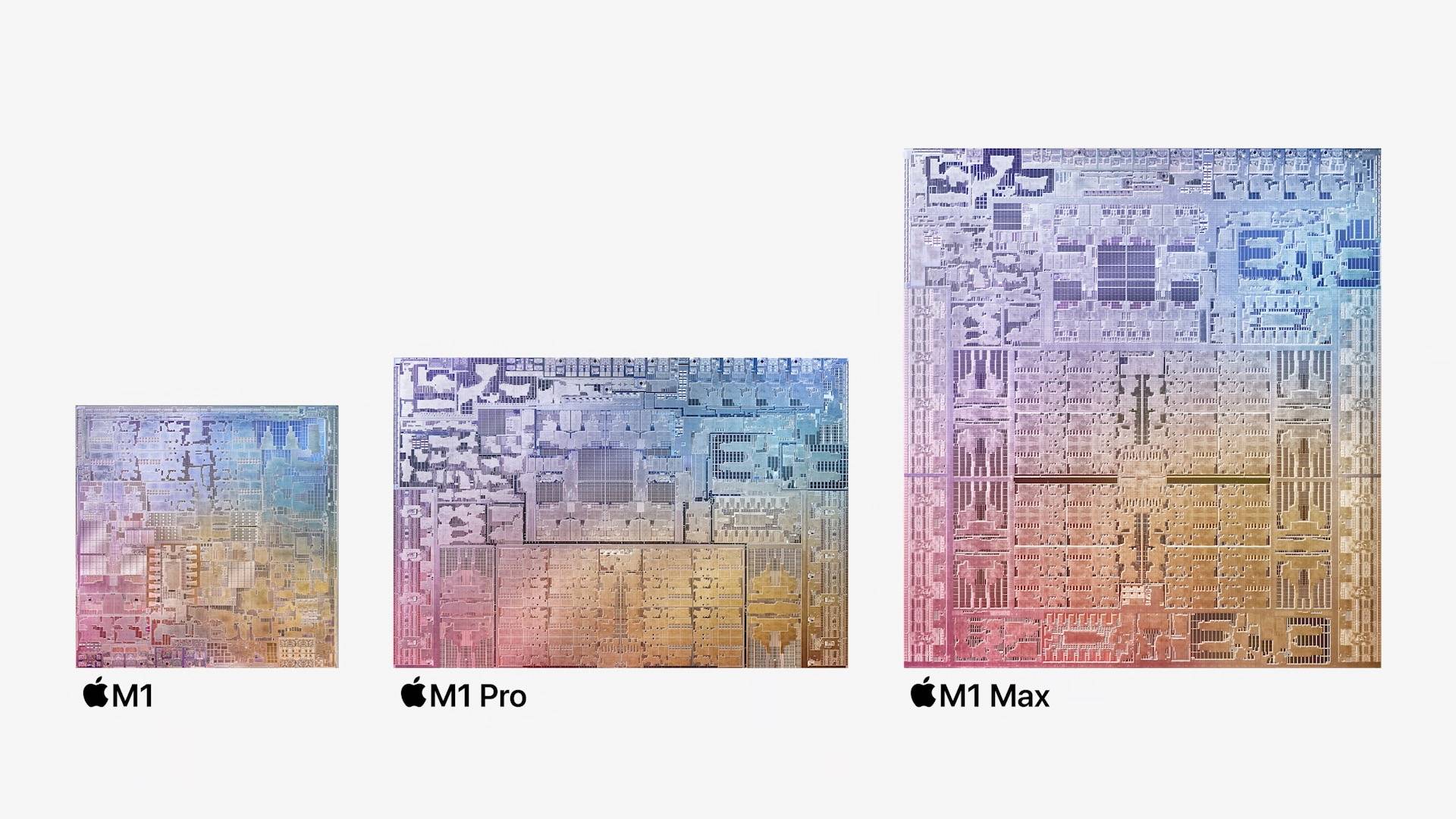

Du M1 aux plus puissants M1 Pro et M1 Max, ils ont quasiment la même architecture. La sortie de performances du single core est relativement proche. La plus grosse différence est en fait le nombre de cores.

Même, vous pouvez simplement comprendre que les puces M basées sur ARM reposent sur le nombre de cœurs de tas pour obtenir un plafond de performances plus élevé.

- M1 : CPU 4+4 cœurs, GPU 8 cœurs, 16 milliards de transistors, réseau de neurones à 16 cœurs ;

- M1 Pro : CPU 2+8 cœurs, GPU 16 cœurs, 33,7 milliards de transistors, réseau de neurones 16 cœurs ;

- M1 Max : CPU 2+8 cœurs, GPU 32 cœurs ; 57 milliards de transistors, réseau de neurones à 16 cœurs ;

D'un autre point de vue, la surface de puce de M1 est d'environ 120 mm², tandis que celle de M1 Pro est de 245 mm². En ce qui concerne M1 Max, elle monte directement à M1 Max 432 mm².

Pour la même génération de puces M, plus il y a de Max, plus le nombre de cœurs et la surface de la puce sont importants. À partir de là, il n'est pas difficile de comprendre les règles de dénomination d'Apple pour les puces M. C'est facile à comprendre. Microsoft, Intel et Qualcomm devrait vraiment étudier dur.

Bien que Tim Millet, architecte et vice-président des puces d'Apple, ait expliqué en détail sur le podcast Upgrade en novembre, le travail acharné d'Apple dans le développement de la puce M, mais pour le prochain développement de la puce M, et Comment changer Max sur la base de Max n'a pas prononcé un mot.

▲ L'architecte et vice-président des puces Apple Tim Millet (Tim Millet).

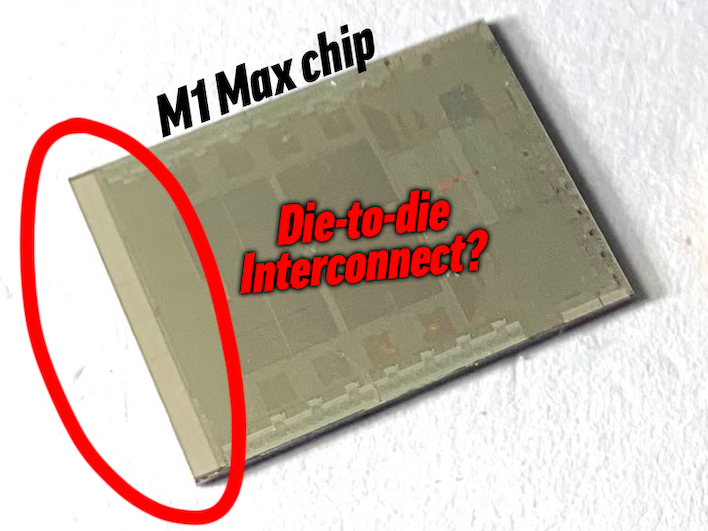

Avec les MacBook Pro 14/16 sur le marché les uns après les autres, après de nombreuses explorations de bricoleurs privés, il semble qu'Apple ait également fait du M1 Max une préfiguration plus Max.

C'est "Mettez deux M1 Max, et vous pouvez même le doubler."

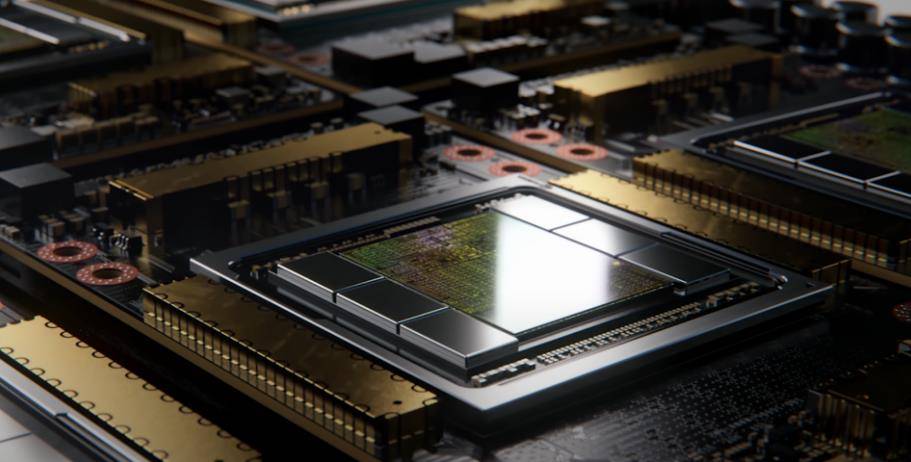

Zone cachée M1 Max. Image de : HothardWare

Cette conjecture est en fait basée sur le démontage et a constaté que le M1 Max a une "zone inconnue" supplémentaire par rapport au M1 Pro. Après quelques réflexions, on suppose qu'il s'agit d'un "bus à grande vitesse" réservé à la connexion de deux ou plus M1 max.

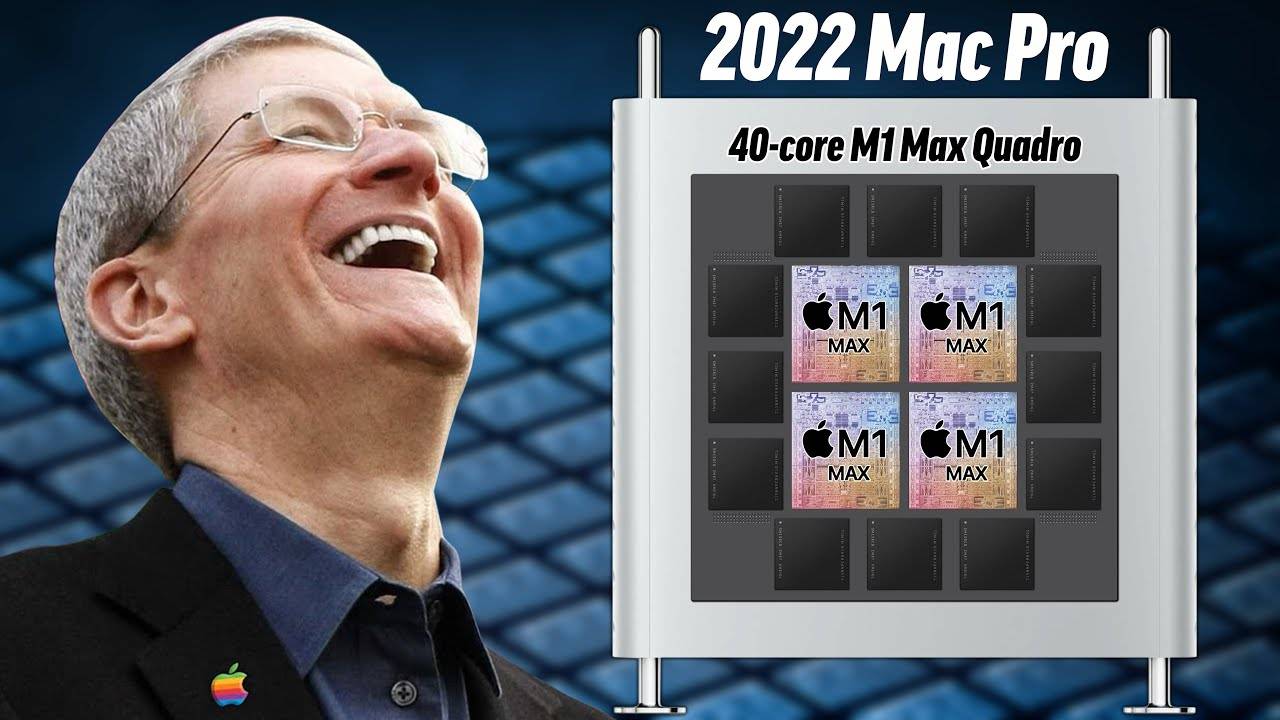

▲ Tim Cook : Intel, ceci est pour vous. Photo de : Max Tech

Cela correspond également aux rumeurs selon lesquelles les nouveaux iMac Pro et Mac Pro utiliseraient plusieurs processeurs M1 Max. "C'est comme jouer aux Lego, empiler du bois et frapper le maître sans discernement."

Cependant, le terme « tas de bois » n'est pas très précis, et « puzzle » est plus précis. De cette façon, la surface de puce du double M1 Max sera assez considérable, et quatre fois c'est sans précédent.

Le M1 Max Duo surpasse le meilleur GPU GA100 de Nvidia.La surface de la puce (826 mm²) est presque certaine.

Un SoC aussi énorme, en regardant toute l'histoire des semi-conducteurs, peut certainement être considéré comme une puce de niveau "Tyrannosaurus", sans parler du fait qu'il sera basé sur un processus de 5 nm, et le coût est très susceptible de dépasser n'importe quelle puce contemporaine.

Quand les puces de la série M entrent dans "Jurassic Park"

De l'ordinateur d'origine ENIAC pesant 30 tonnes et couvrant une superficie de 170 mètres carrés, au PC de bureau actuel, presque tous les équipements évoluent vers la miniaturisation et l'intégration.

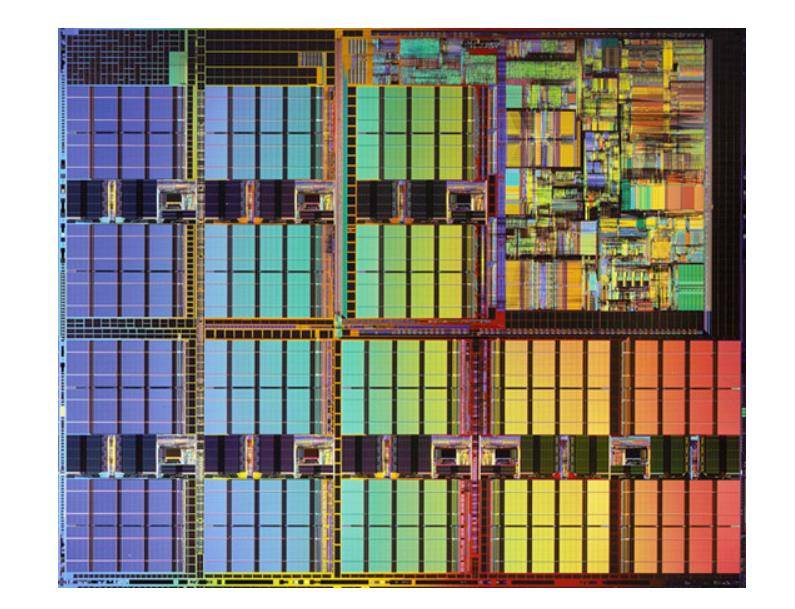

Il en va de même pour les processeurs du monde des semi-conducteurs. Lorsque le nœud de processus est encore de m, la surface du premier Pentium d'Intel (Pentium) est d'environ 294 mm², sur la base du processus de 0,8 m.

Intel Pentium III Xeon.

À l'ère des processeurs x86, Intel Pentium III Xeon a une superficie de 385 mm² et repose sur un processus de 0,18 µm. Cependant, à cette époque, de nombreux fabricants de processeurs contrôlaient strictement le volume et supprimaient les coûts et introduisaient des PC relativement abordables pour les promouvoir auprès du grand public.

À l'avenir, qu'il s'agisse de la popularité du 64 bits ou du bond des nœuds de processus, la taille du processeur est principalement contrôlée en dessous de 500 mm².Sous le principe du contrôle des coûts et de l'utilisation efficace des plaquettes, il a presque arrêté le consommateur. processeur de qualité de faire face à la "dinosaurisation". "développement de.

L'industrie des semi-conducteurs grand public semble être progressivement passée du Jurassique à une nouvelle ère.

▲ Les dieux populaires font également des suggestions pour le développement de la puce M d'Apple. Image de : Twitter

À l'heure actuelle, la voie de développement possible de la puce M d'Apple semble s'être enroulée vers le "Jurassique", mais si la taille du processeur a avancé, la densité des transistors n'a pas baissé.

Bien qu'il semble qu'il ne devrait pas être difficile de mettre deux puces ensemble, et qu'il n'est pas nécessaire de reconcevoir l'architecture et le noyau. Mais en réalité, avec l'augmentation de la surface des copeaux (surtout le doublement de la croissance) et la garantie d'un rendement et d'une capacité de production suffisants, le coût décolle directement.

Les puces de la série M d'Apple sont toujours des produits de consommation.Il y a un an, ils se sont débarrassés d'Intel, d'une part pour contrôler la force du produit, d'autre part, pour contrôler les coûts et maximiser les profits. Le coût erratique d'un SoC à grande surface n'est clairement pas ce à quoi Apple s'attendait.

▲ La mémoire unifiée la plus élevée de M1 Max est de 64 Go, alors M1 Max Duo passe directement à 128 Go ?

D'un autre côté, si deux M1 Max ou plus sont épissés ensemble, la conception de la mémoire unifiée (UMA) sera également un énorme problème. Replanifiez l'emplacement du multicœur, introduisez une bande passante plus large et une capacité plus élevée. la mémoire, c'est inévitable.

Pour le public, il peut s'agir d'une conception de puce plus compliquée, et pour le privé, cela peut augmenter de manière invisible le coût plusieurs fois, ce qui sera deux pierres d'achoppement majeures pour que la puce M d'Apple devienne plus Max.

La loi de Moore est dans le passé, le moment est maintenant

« Le nombre de transistors pouvant être logés sur un circuit intégré doublera environ tous les deux ans. » C'est la célèbre loi de Moore, et elle a un autre dicton : « Tous les 18 mois, les performances de la puce doubleront. »

▲ MacBook Pro 16. Image de : dpreview

Les performances ici se réfèrent en fait au nombre de transistors.Par rapport à M1, M1 Max a une amélioration des performances de 3,5 fois, ce qui reflète simplement la différence de nombre de transistors.

Le nombre de transistors a doublé dans la série M1, ce qui représente une augmentation de la surface de la puce. D'un point de vue historique, il est plus dépendant des progrès technologiques, du niveau μm au nm, le nombre de transistors a également bondi d'un million à cent millions.

Cependant, vers 2013, la loi de Moore a ralenti. Depuis lors, les avantages en termes de performances de l'amélioration des nœuds de processus ont diminué.

Des procédés technologiques plus avancés peuvent en effet augmenter le nombre de transistors, mais ils s'accompagnent également d'évolutions de coût et de rendement.

TS TSMC devrait commencer la production du procédé 3 nm en 2023. Photo de : anandtech

Selon les données publiées par l'International Business Strategy Corporation (IBS), la conception d'une puce 3 nm devrait coûter 590 millions de dollars américains, tandis que 5 nm ne coûte que 416 millions de dollars américains, 7 nm 217 millions de dollars américains et 28 nm ne représentent que 40 millions de dollars américains. dollars.

TSMC a précédemment annoncé qu'il investirait 20 milliards de dollars américains pour construire une usine de plaquettes de 3 nm, également pour 3 nm, le coût de Samsung n'est pas inférieur à celui de TSMC.

Jusqu'à présent, seuls TSMC et Samsung déploient activement des plaquettes 3 nm. D'autres fabricants ne veulent pas, mais ne peuvent pas se permettre l'argent.

D'autre part, le taux de rendement des copeaux diminue à mesure que la surface augmente. Le taux de réussite de conception de 700 mm² n'est que de 30% environ. Lorsqu'il est réduit à 150 mm², le taux de rendement s'élève à 80%.

Peu importe comment vous le regardez, la route vers les mises à niveau des puces semble avoir été bloquée.

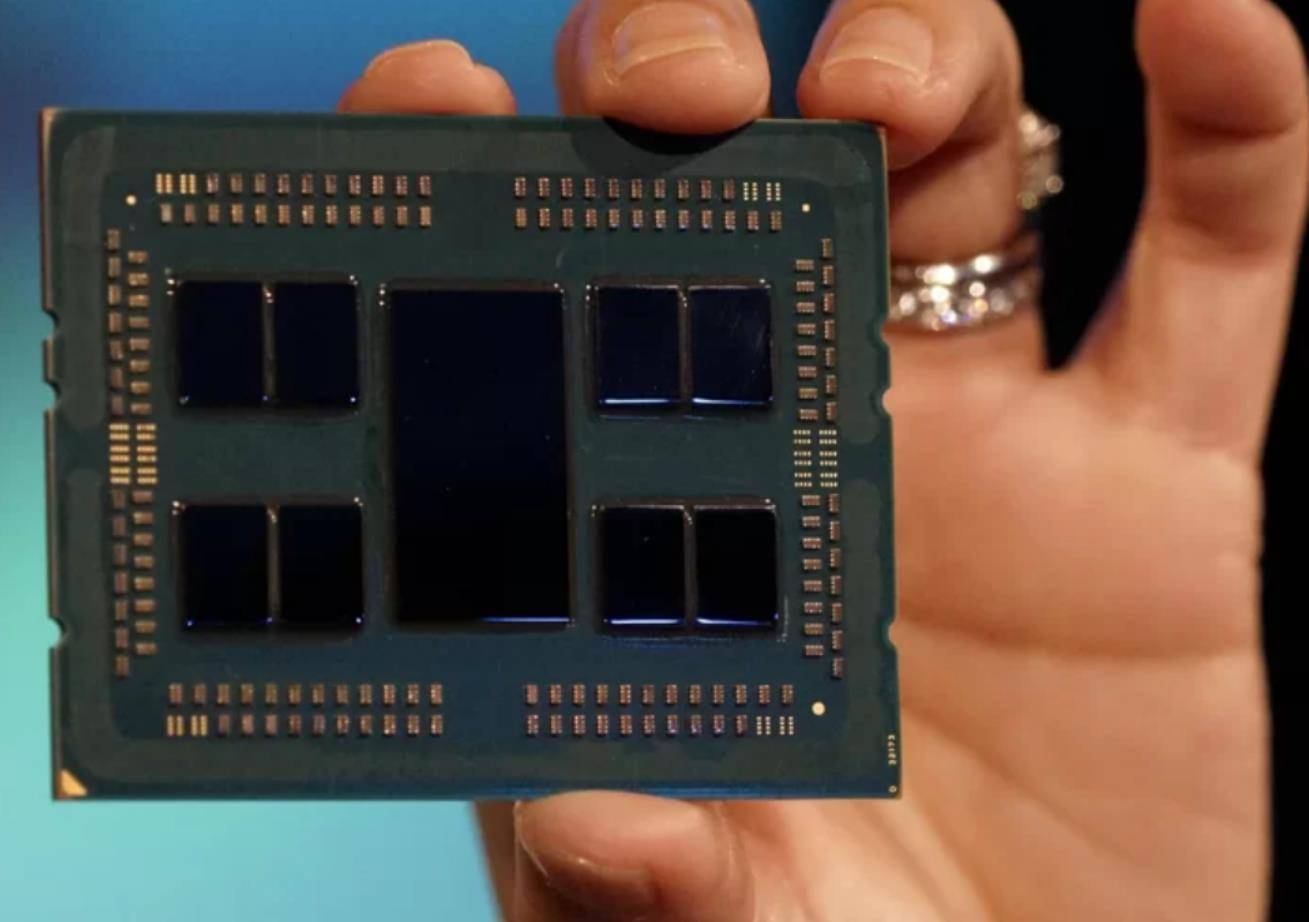

▲ Processeur AMD EPYC 2 (Rome) basé sur Zen 2. Image de : AMD

Afin de continuer à augmenter l'échelle et la densité des puces, de nombreuses personnes ont détourné leur attention de la mise à niveau du nœud de processus vers le processus de conditionnement, qui est la technologie Chiplet (petite puce) d'AMD.

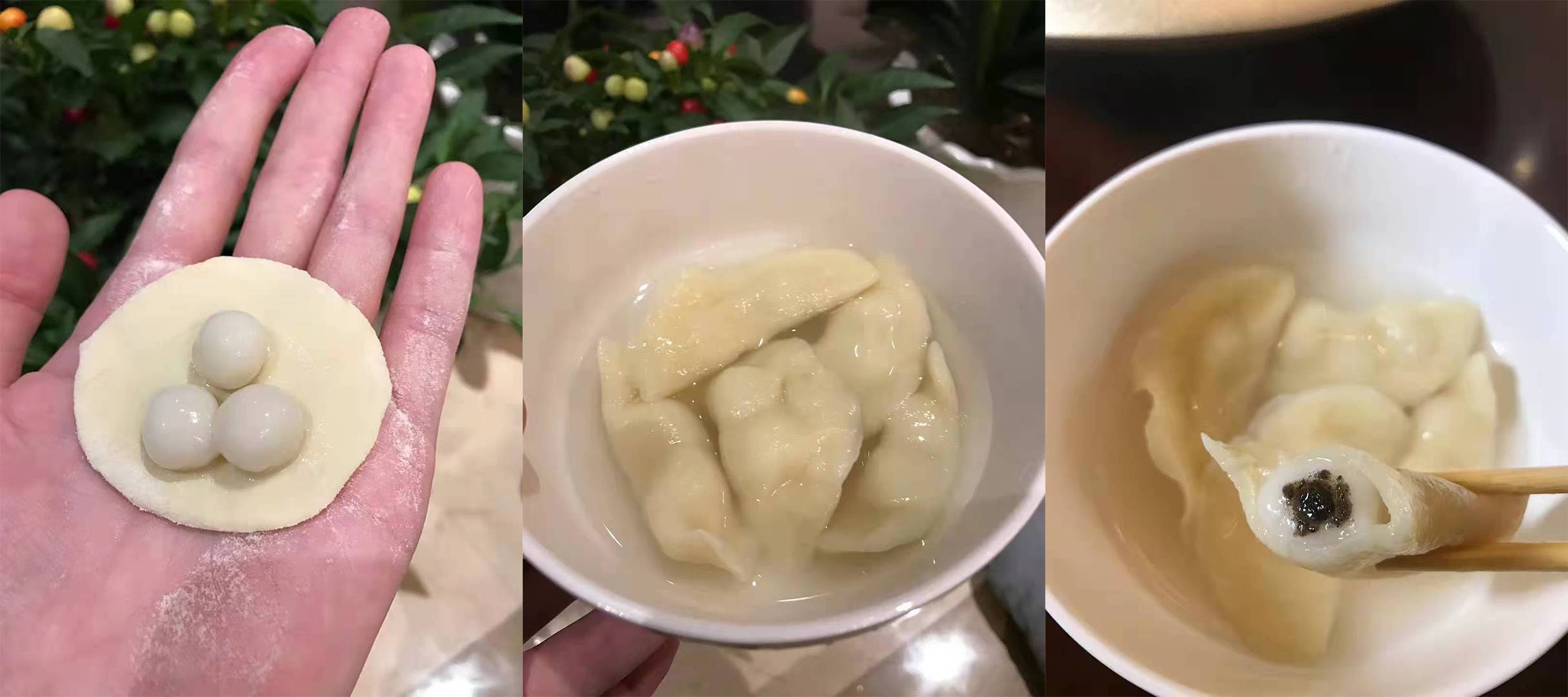

En termes simples, Chiplet est comme des boulettes remplies de boulettes de riz gluant, encapsulant ensemble de petites chips avec différentes fonctions, au lieu de couper directement à partir de la plaquette, et utilisant une technologie d'emballage avancée pour compenser la stagnation du nœud de processus.

▲ Actuellement la métaphore la plus frappante pour Chiplet (mais je n'approuve pas cette façon de manger).

Au cours des dernières années, AMD a également utilisé la technologie Chiplet pour augmenter continuellement la densité du processeur afin de contre-attaquer Intel, et a progressivement commencé à s'emparer du marché.

Pour Chiplet, qui a émergé ces dernières années, The Linley Group, une organisation de conseil faisant autorité dans l'industrie technologique, a directement proposé que Chiplet puisse réduire le coût de conception des grandes puces 7 nm de plus de 25 % dans l'article "Pourquoi les grosses puces obtiennent Petit". Au cours du processus, les économies de coûts seront encore plus importantes.

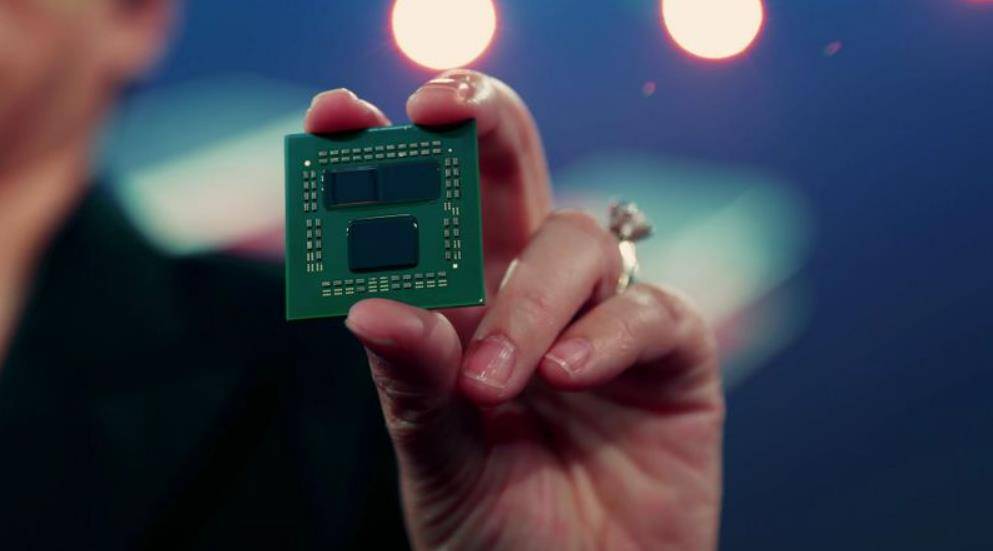

▲ AMD est basé sur le processeur Ryzen 9 5900X dans un package Chiplet 3D.

Et le V-Cache 3D annoncé par AMD confirme également que Chiplet, qui combine l'ancien processus et le processus d'emballage avancé, peut atteindre des performances de nœud plus élevées, et même mélanger des puces de différents nœuds de processus, avec suffisamment de flexibilité.

En plus de réduire les coûts et d'atteindre des performances plus avancées, Chiplet accélérera également les lancements de produits.Après tout, il suffit d'utiliser directement d'anciennes puces avec des processus d'emballage avancés, et même d'ignorer la disposition des nœuds de processus avancés.

Ayant dit tant d'avantages, Chiplet a également des inconvénients correspondants. L'empilement de petites puces 2D et 3D a des exigences très élevées pour la conception de la gestion thermique, et la consommation d'énergie thermique totale dans le boîtier sera considérablement améliorée.

▲ Puce de serveur Intel basée sur Chiplet. Image de: nextplatorm

Mais dans tous les cas, Chiplet a été reconnu par de nombreuses institutions et fabricants comme une technologie importante pour des percées continues dans les performances des puces dans l'ère post-Moore.

▲ M1 à l'intérieur du Mac mini et du MacBook Air.

Pour en revenir à la puce M originale développée par Apple, grâce à l'architecture ARM et à la mise à niveau des nœuds de processus, le taux d'efficacité énergétique est continuellement amélioré et le rendement et le coût sont contrôlés en passant. Quant à savoir s'il combinera plusieurs M1 Max pour former un SoC géant complexe dans un Mac Pro au niveau du poste de travail, du point de vue actuel, Apple a suffisamment de capital et de force pour concevoir et produire un processeur "béhémoth préhistorique".

▲ Rendu non officiel de l'iMac Pro 2022.

Quant à Chiplet, je pense qu'il a dû apparaître dans les dessins de l'équipe puce d'Apple. Au lieu de faire face à la future mise à niveau incertaine du nœud de processus, il est préférable de rechercher activement des changements et de s'appuyer sur la puce M actuelle et la puce A à combiner pour compléter une mise à niveau plus profonde du SoC.

#Bienvenue pour suivre le compte WeChat officiel d'Aifaner : Aifaner (WeChat ID : ifanr), un contenu plus passionnant vous sera fourni dès que possible.

Ai Faner | Lien original · Voir les commentaires · Sina Weibo